摘要:现在社会是一个电子信息化快速发展变更的社会,特别是近年来随着计算机科学技术的惊人发展,数字电路的研究每一天都在突破和更新。越来越先进的电子技术不断被人们研究出来并应用于实际生活中,给人们的生活带来极大的方便,让人们享受电子技术给生活带来的便捷。数字集成电路的设计方法也被越来越多的人们不断的探寻和研究,希望能够创想出新的思路和方法,推动相关行业的发展。

关键词:数字集成电路;集成电路的设计方法;数字电路研究

1.数字电路的发展

数字电路在我国得到发展,是在近30年才得到飞速发展的。最早的数字电路是人们使用电子管和晶体管搭建而成,无论是在结构上还是使用上都有很大的不便,一直到有人能够将逻辑顺序的逻辑门做到单芯片,出现这种技术的时候才出现了最初的集成电路。最早的集成电路也只是很有限的几个少门数,小规模集成电路。但每一天人们都在不断的研究和改进,随着时间的发展,集成电路也出现了一些非常大的变化,几百门甚至几千门的规模集成电路被人们研究使用。从这一时候起,人们使用的集成电路设计开始变得复杂,而且人们也发觉了集成电路自动化的必要性,传统的在面包板上的进行验证电路的道路已经变得落后和不太可能,这时计算机的辅助技术成为设计和验证规模更加超大的集成电路(VLSI)的一个非常关键的技术。

2.芯片系统的设计

在伴随着集成电路中深亚米制造技术的不断发展,人们对数字电路的设计也得到了很大的改进,传统的集成电路开始进一步的应用在片上,也就是最初的片上系统,系统初级芯片,就是系统集的集成电路,给现在的数字集成电路奠定了基础。系统及电路集成系统缩写为SOC(System on a chip),也可以写成SLI(System Level IC)。在系统集的数字集成点路上,能够在每一个单一芯片实现信号的采集、转换、存储和进一步的处理以及I/O等各种功能,从而将这一个系统电路功能进行实现。这一巨大的改变,突破了传统的不足,变得更加高速,高集成度和更低功耗,是一个巨大的飞跃性的发展,并且大大的降低了整机的成本,体积,加快了整机系统的更新速度。最明显的体现就是电脑,手机,MP3等便携设备的更替。

2.1芯片系统困难的解决

想要做好系统集集成电路有一个必要的条件之一,那就是的它的线宽必须要能够达到深亚微米级别。然而在当代的SOC芯片中大多数都只0.25um~0.18um的设计规则,这就使得传统的技术在这里完全不适用,SOC芯片的设计有了新的困难。而且集成电路设计在进一步进入到深亚米阶段后,它的特征尺寸缩小,横向和纵向尺寸也都大大的多小了很多。与之相反的是芯片内的互连线长度却是增大了几倍,这时互连线与线之间的电阻对电容信号的传输有着非常明显的影响,不利于信息的传递。这就给SOC和EDA(电子设计自动化)提出了新的挑战。

为了解决这一困难,在初期获得有关互连线的信息,人们在目前经常采用的一种方法是加入了布局规划,合理的使用布局规划对电路进行有效的预期布局,并且在这一过程中能够有效的得出电路互联延迟的估计状况,然后这些估计状况就成为了一种经验,为后续的电路发展提供宝贵的经验。不过这一种方法在实际的应用中存在着一些不足,它在布线规划中很难真正的保证电路之间能够最大程度的互延迟时间的准确程度。而且在另一方面,由于在设计的初期对线路进行了预估,对电路的物理位置形成了进一步的约束,导致在一定程度上对电路的优化形成影响。

3.HDL语言的发展和应用

在最近的十几年来,硬件描述语言(HDL)在以往的逻辑电路中得到了很好的应用,促进了逻辑电路设计的发展。在使用硬件描述语言的时候,设计者能够更好的遵从自己的医院从功能和行为上对自己详细的表述自己的设计过程和设计理念,而且还可以加上详细的注解,使得在以后的使用中重复使用。

3.1HDL语言的种类和使用

硬件描述语言(Hardware Description Language)的缩写就是HDL,HDL的发展速度很快,并且也有很多种。但是在日常的生活中人们经常使用到的有Verilog(模块)HDL和VHDL(Very High Speed Integrated Circuit HDL的缩写)。这两种被人们在日常生活中广泛的使用有着多种多样的原因。

前者Verilog HDL是CAD公司在1983年的时候建立起来的,它的基础语言是C语言,演化成的硬件描述语言结构简单易读,而且非常便于人们学习和掌握,它与C语言的编程非常的相似,初期只是公司的私有财产,在很晚的时候才标准化,规定化。

后者VHDL是ADA语言发展的,而且这一语言在当时收到了美国国防部的大力支持,在1978年时就已经成为了一个标准,但是由于它的基础语言ADA语言使用者的数量非常的少,所以并没有被人们广泛使用,传播的数量也远远没有C语言多,普及程度没有C语言高。

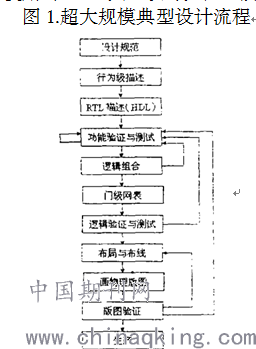

在目前,人们使用的HDL典型设计如图1所示

在任何的一项设计中,最先要进行的就是能够写出设计规范,因为一个完整的合理的设计规范能够形象的描述设计项目电路的每一个功能,接口以及整体结构的完整性。在设计电路的过程中我们通过对电路的功能进行详细的分析我们可以了解到,所设计的电路它的性能以及我们要研究和解决的其他高级问题。然后我们才能够进一步的进行行为级的描述,也就是用硬件描述语言来进行撰写活动。

4.逻辑问题的研究

行为级描述完成后,需要进行优化和功能仿真,在目前所拥有的电子设计自动化EDA工具只能够对RTL级描述的HDL文件进行自动逻辑的综合,因而需要将行为级描述用手工的方法转换成寄存器传输级(RTL)的HDL描述,然后把RTL再次进行仿真验证。然后再接下来的程序中合理使用CAD工具完成。

在整个逻辑程序里,我们实现将代码映射到具体工艺上,然后实现我们实验逻辑的仿真。逻辑综合工具能够把RTL描述转换成门级网表,转化后的门级网表示门电路以及门电路之间连接描述的一种方式,对产生版图而言有着十分重要的作用。

在使用版图工具产生版图,确定了版图的布局和布线等方式以后,我们就能够从版图里提取出相关的连线电阻,电容等一些数据和参数。把从版图中提取到的参数标到门级网表中,然后我们再次进行门延时、连线、延时等门级仿真,一般人们把它称作为后仿真,主要目的是为了能够进行有效的时序模拟。如果在进行最后的时序程序不能够运行下去的时候,那么我们便需要仔细的分析整个实验过程,往前者逐级寻找错误修改,直至整个程序能够合理的运算下去,最后将得到验证后的版图直接坐到硅片上进行使用。

5.结束语

随着互联网的普及,中国经济水平的快速提高,人们掌握的先进知识也越来越丰富。我相信在不久的将来,人们在数字集成电路这一方面会有更加先进,智能的工具和方法,目前所遇到的各种问题和技术瓶颈也能够得到解决和突破,人们能更加快速准确的制造出实用的电路,促进行业整体的发展和人民生活水平的提高。由于笔者水平有限,文中存在的不足之处敬请相关专业人员和广大读者谅解,也希望本文能够给所需要的人带来一定的帮助。

参考文献:

[1] 沈戈,基于可重用IP的SOC设计方法学的研究,西安石油学院学报(自然科学版),2003,20~24

[2] 白中英,计算机组成原理,北京:科学出版社,1994

[3] 魏少军,SoC设计方法学,电子产品世界,2001,13~16

[4] 郑纬民、汤志忠,计算机系统结构(第二版),清华大学出版社,1999年7月

[5] Bob Zeidman,Verilog Designers Libarary,Prentice Hall PTR,1999

论文作者:刘禹延

论文发表刊物:《电力设备》2017年第18期

论文发表时间:2017/11/6

标签:集成电路论文; 电路论文; 语言论文; 这一论文; 版图论文; 逻辑论文; 系统论文; 《电力设备》2017年第18期论文;